# **TETRACOM: Technology Transfer in Computing Systems**

FP7 Coordination and Support Action to fund 50 technology transfer projects (TTP) in computing systems. This project has received funding from the European Union's Seventh Framework Programme for research, technological development and demonstration under grant agreement n<sup>o</sup> 609491.

# Functionality assignment to partitioned multi-core architectures

Florin Maticu and Paul Pop, Technical University of Denmark Christian Axbrink and Mafijul Islam, Volvo Group Trucks Technology

**TTP Problem**

Motivation

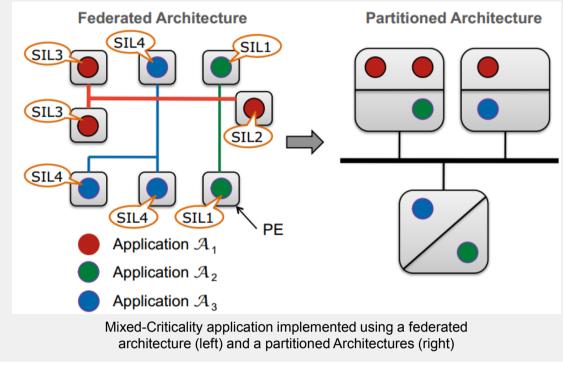

Federated to partitioned architectures

Multi-core ECUs

Such that we want to minimize:

- Increase complexity of software functionalities.

- Safety according to ISO 26262

- Schedulability of tasks running of different

cores

Bus bandwiths utilization

**Problem Formulation**

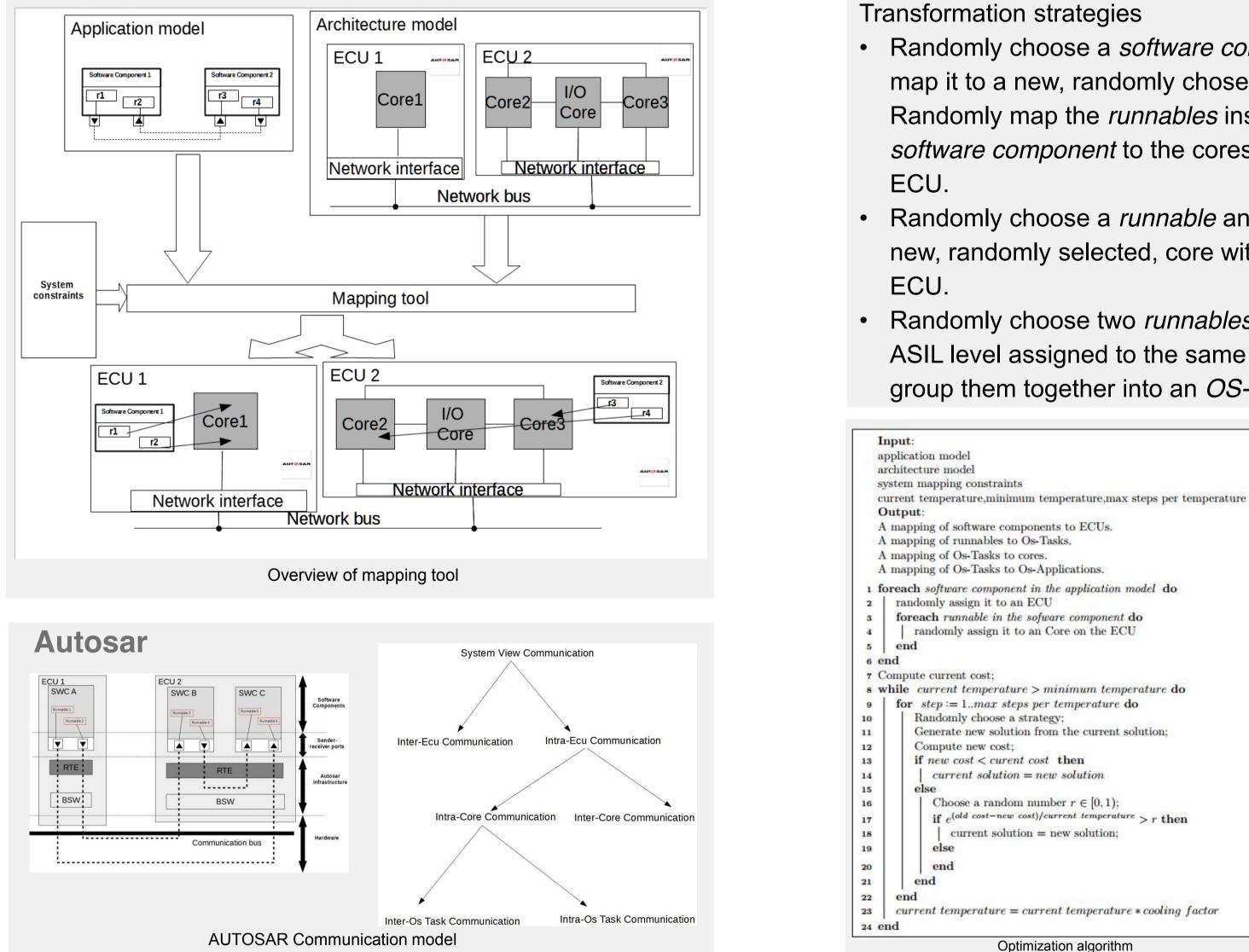

Given an application model and an architecture model we want to determine :

- A mapping of *software components* to ECUs

- A mapping of *runnables* to cores

- A mapping of *runnables* to *OS-Tasks*

- A mapping of *OS-Task* to *OS-Applications*

- The overall communication bandwidth

- The variance of core utilization of the system

Taking into consideration that:

- Mapping constraints, if specified, are satisfied

- The *runnables* are schedulable (U < 0.69)

- The *runnables* with different safety integrity levels are spatially and temporally isolated.

### Mapping Optimization

NP-Hard problem, so Simulated Annealing based optimization strategy is used which searches, using transformations, for solutions minimizing a given cost function.

## Cost function:

## **TTP Solution**

- Randomly choose a *software component* and map it to a new, randomly chosen, ECU. Then Randomly map the *runnables* inside the software component to the cores of the new

- Randomly choose a *runnable* and map it to a new, randomly selected, core within the same

- Randomly choose two runnables of the same ASIL level assigned to the same core and group them together into an OS-Task.

Where :

- $W_1$  and  $W_2$  denotes weights

- $P_1$  and  $P_1$  denotes penalties

- $\sigma$  the total *variance* in core utilization

- $U_b$  the aggregated bus utilization

- $\alpha$  denotes the amount of cores which utilization has been exceeded

- $\beta$  denotes the amount of busses which utilization has been exceeded

# **TTP Impact**

The tool will allow Volvo to reduce the costs (by using multicores and reducing the number of ECUs), maximize performance and resource utilization and handle the increased software complexity.

### Example

- Input : Application Model

- Input : Architecture Model

- Output : Mapping

## **Expected added value from the technology transfer**:

Efficient utilization of multicores and compliance with functional safety standard ISO 26262 are among the key

http://www.tetracom.eu | @TetracomProject