Multicore Platform SW Optimization with the MAPS Compiler

Mobile networks and devices have changed the landscape of human communications completely. The recent cellular evolution including 3G data services, 4G broadband coverage boasting speed even faster than DSL/Cable and upcoming 5G standards demands advanced hardware architectures and software support that have never been tougher in the wireless community. It is strongly argued that the architectures have to be multicore and heterogeneous due to performance and energy reasons. However, one of the biggest hurdles to further exploit multicore architectures is how to efficiently develop parallel software, especially given the rising complexity of today’s systems.

In this TTP, we are focusing on designing next generation of wireless base stations. The complexity of such systems is growing exponentially because:

- Significantly more computing power is required to meet upcoming industry wireless standards.

- Not only timing as a performance goal is sought of now. It is fairly common that power / energy are used as co‐optimization goals.

- Application dynamism must be taken into consideration during design cycles. Particularly for wireless base stations, multi‐mode capability and scenarios that represent considerably different working loads are typical examples.

Huawei, as a leading telecom solutions provider, faces such challenges. The purpose of the TTP is to investigate the use of RWTH ICE’s MAPS compiler technology in software development for Huawei´s multicore SoC platforms for wireless baseband processing. The general goals are to increase SW development productivity, quality of results, and portability across a range of Huawei SoC platforms. Please note that this TTP covers partially the period of the whole collaboration project between RWTH and Huawei.

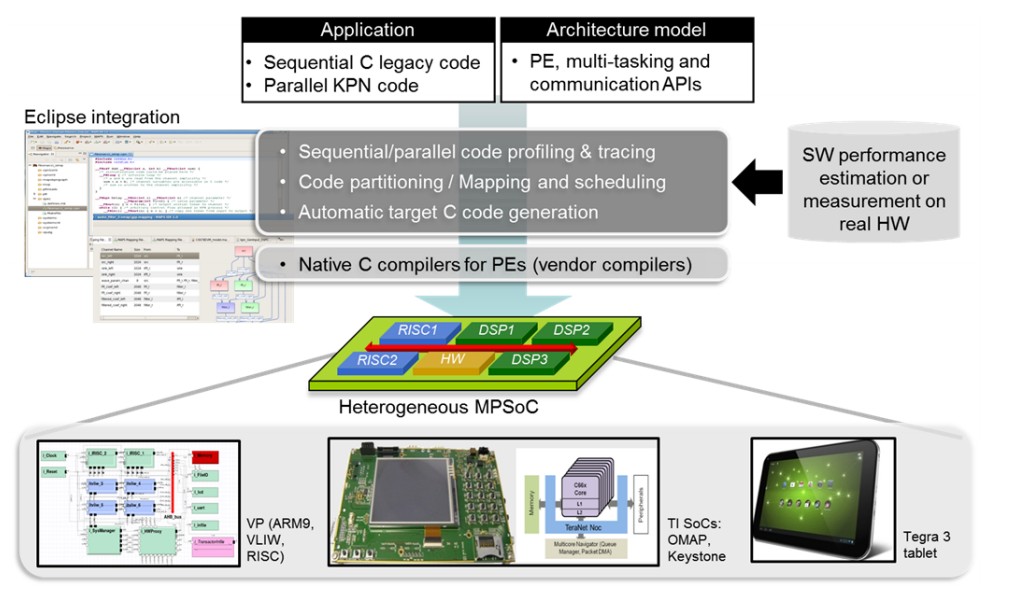

The MAPS compiler flow works as sketched in the figure above. The main inputs are application specifications either in sequential C language or ICE´s proprietary C language extension CPN (C for Process Networks) language, which follows the widespread SDF and KPN models of computation. Another input is an XML specification of the target architecture and its APIs, which enables portability (and optionally architecture exploration and optimization). The entire MAPS compiler is operated via a user‐friendly Eclipse based GUI. Based on the chosen application specification, MAPS supports two major use cases: The sequential flow for mapping C programs into parallel formats suitable for parallel mapping, and the parallel flow for optimized spatial and temporal CPN mapping to the target SoC. Internally, the MAPS compiler uses a multitude of advanced code partitioning, task and communication mapping, profiling, and performance estimation techniques in order to generate the best mapping of the input application to the given target SoC platform.

In the TTP, a wireless target SoC platform close to the Huawei product is chosen and a number of selected LTE physical layer processing applications are used as benchmarks. During the TTP, a simulation platform is built as verification and first‐order performance measurements. Some components in the current MAPS flow (middle end and backend) are adapted to the target platforms as well as a high‐level architectural description to model the platform’s performance characteristics and other metrics is developed. The code generation engine in the MAPS backend is also retargeted for the selected SoC and the corresponding APIs. A large chunk of the TTP period is devoted to understand the Huawei in‐house LTE physical layer applications and model them using the CPN language of the MAPS framework. This turns out to be a good practice to see if the academic research results could be applied in industrial environments – some extensions are made to accommodate Huawei specific requirements. While the final results of the project are still in the making, in the TTP phase RWTH has successfully delivered the MAPS training on‐site at Huawei, the initial tools and the simulation platform.